article detail

최적화 AI 모델로 통신반도체 설계 시간 76%↓

2026. 5. 5. 오전 10:47

AI 요약

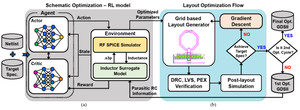

울산과학기술원(UNIST) 윤희인 전기전자공학과 교수팀이 송대건 경북대 교수팀과 함께 LC 전압제어 발진기(VCO) 회로 설계 이후 칩 레이아웃까지 자동 설계하는 AI 모델을 개발했다고 5일 밝혔습니다. 이 모델은 강화학습으로 회로 설계 변수를 최적화하고 레이아웃 단계에서는 경사하강법으로 배선 폭 등 물리적 설계 변수를 보정해 기존 119시간 소요 작업을 28.5시간으로 단축해 설계 시간을 76% 줄였고, 반복적 전자기 시뮬레이션을 몇 밀리초(ms) 만에 완료했습니다. 연구 결과는 국제학술지 전기전자공학자협회(IEEE) 집적회로 및 시스템 설계자동화에 지난달 3일 공개됐으며, 연구팀은 이 기술을 아날로그·무선주파수(RF) 회로 설계 자동화까지 확장할 계획이라고 밝혔습니다.